GTC2024 春 基調講演レポート 特別寄稿 笠原一輝

二つのダイを1パッケージにして生成AIに最適化されたアーキテクチャを採用したNVIDIA新GPU「Blackwell」

NVIDIAは3月18日~3月20日(現地時間)に、米国カリフォルニア州サンノゼのサンノゼコンベンションセンターにおいて、同社のフラッグシップ年次イベント「GTC」を開催した。

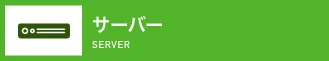

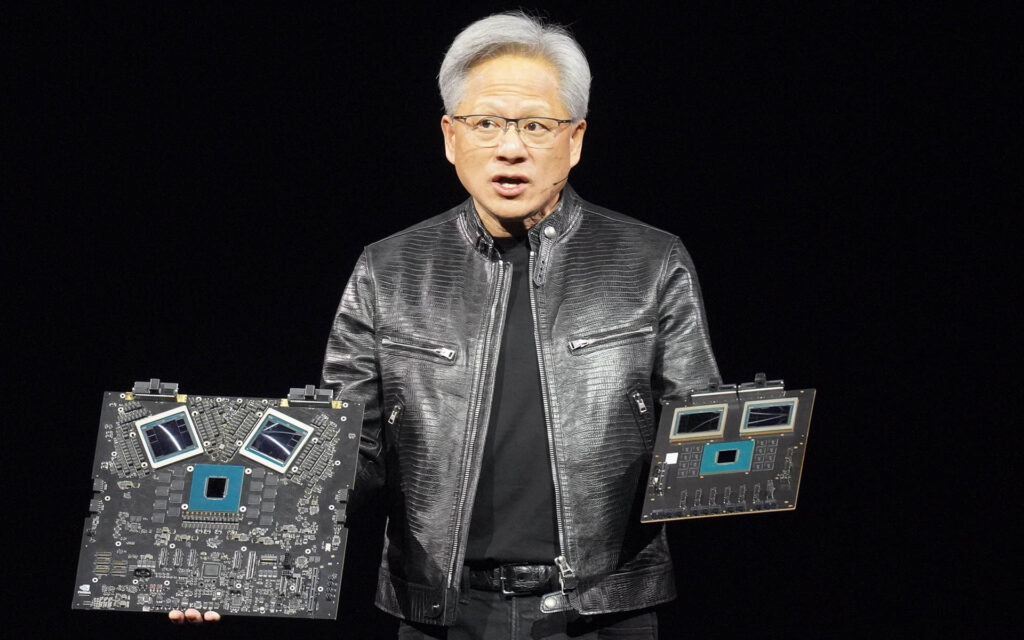

3月18日の午後(現地時間)に行なわれたNVIDIA 共同創始者 兼 CEOのジェンスン・フアン氏はGTCの基調講演に登壇し、同社が開発を続けてきた新GPUアーキテクチャ「Blackwell」(ブラックウェル)の詳細を説明した。この中でフアン氏は「われわれは生成 AI 時代のプロセッサーを作った」と述べ、一昨年11月にChatGPTがリリースされて以来続いている生成AIのブームという一種の社会現象の中で高まり続けているGPUへのニーズを満たすような新製品になっていると強調した。

実はフアン氏のこの一言は、Blackwellの特徴を一言で物語っている。今回NVIDIAはBlackwellを設計する上で、生成AIの処理速度を最優先に設計したと考えられるからだ。

■二つのダイを1パッケージに封入したのがBlackwellの最大の特徴

NVIDIAのGTCが現地の会場において対面方式で開催されたのは、2013年の3月以来となり、実に5年ぶりとなる。2020年の3月に予定されていた、対面方式でのGTCは、その年の1月から全世界的に新型コロナウイルスが流行してきたことで直前に中止となり、その後バーチャル方式で開催されることになった。そのバーチャル方式で行なわれた2022年のGTCで発表されたのが、、開発コードネームHopper(ホッパー)こと「NVIDIA H100 Tensor Core GPU」(以下H100)だ。H100はその前の世代になるAmpereこと「NVIDIA A100 Tensor Core GPU」に比べて製造技術(プロセスノード)が7nmから4nmへと微細化されたことで、トランジスタ数が500億個から800億個に増えたことで、内部の演算器を大きく増やすことで性能を向上させた。

今回NVIDIAの本社(サンタクララ)の近郊になるサンノゼ市で行なわれたGTC 24の基調講演の中で、NVIDIA CEOのジェンスン・フアン氏はそのH100(およびそのHBM3e版となるNVIDIA H100 Tensor Core GPU=H200)の後継製品となる、開発コードネーム「Blackwell」の概要を明らかにした。

| Blackwell(フルスペック) | Hopper(H100 SXM) | |

| プロセスノード | TSMC 4NP | TSMC 4N |

| トランジスタ数 | 2080億トランジスタ | 800億トランジスタ |

| ダイ/パッケージ | 2 | 1 |

| FP64 | 45TFLOPS | 34TFLOPS |

| TF32(Tensorコア) | 2.5PFLOPS | 989TFLOPS |

| FP16/BF16(Tensorコア) | 5PFLOPS | 1979TLOPS |

| FP8/FP6(B200のみ)/INT8(Tensorコア) | 10PFLOPS | 3958TFLOPS |

| FP4(Tensorコア) | 20PFLOPS | - |

| GPUメモリ | 192GB(HBM3e) | 80GB(HBM3) |

| GPUメモリ帯域幅 | 8TB/秒 | 3.35TB/秒 |

| NVLink | 第5世代 | 第4世代 |

| NVLink帯域幅 | 1.8TB/秒(双方向) | 900GB/秒(双方向) |

| NV-Switch利用時最大スケールアップ数 | 576 | 256 |

| TDP | 1200W | 700W |

表1:Blackwellと前世代Hopperのハイレベルの違い(NVIDIA社の資料などより筆者作成)

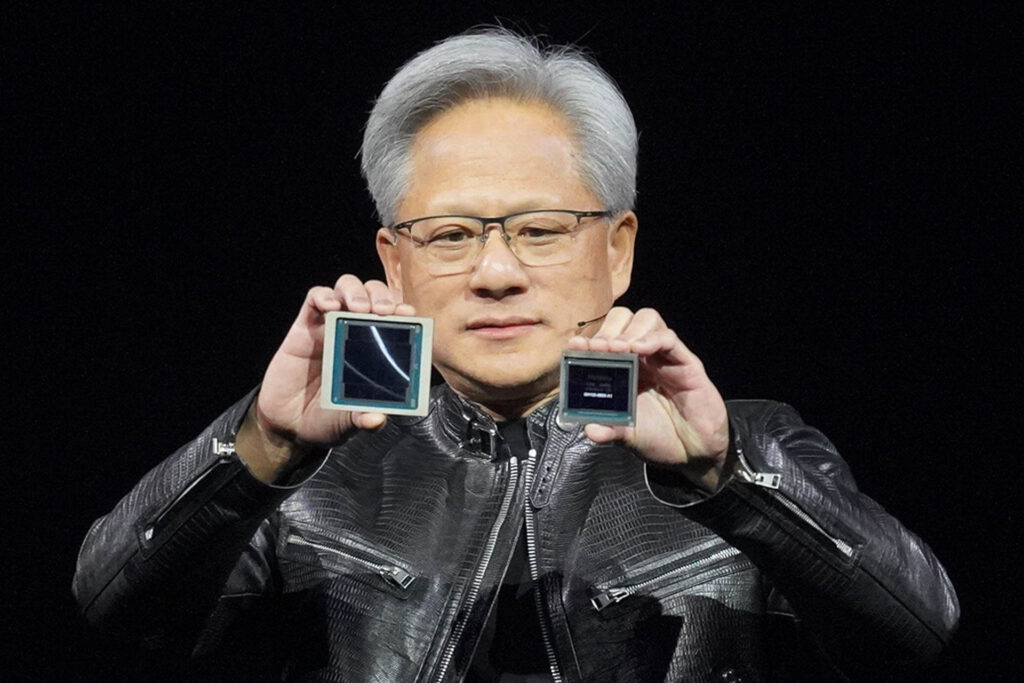

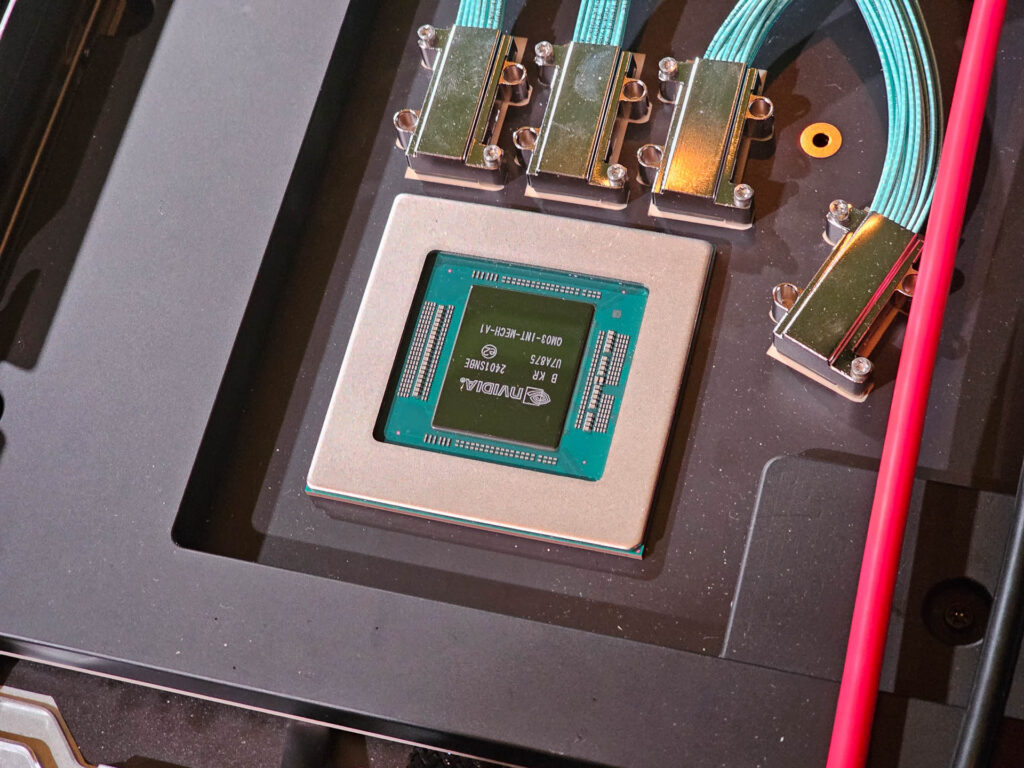

Blackwellの最大の特徴は、二つのダイを1パッケージに封入したことだ。半導体業界ではこうした手法を「チップレット」と呼んでおり、NVIDIAも以前の世代からHBM(High Bandwidth Memory)のチップを、TSMCが提供するCoWoS(コワス)という手法を利用してパッケージ上に封入している。今回はそれを一歩進めて、GPUのダイそのものも複数にする、そうした選択をNVIDIAはしたことになる。

通常チップレットの技術を利用して複数のダイを一つのパッケージに封入する場合、小さめのダイを設計し、それを一つのパッケージに複数個を封入するのが一般的だ。AMDがNVIDIA H100対抗として昨年発表したAMD Instinct MI300Xなどはその典型例で、MI300XはXCDと呼ばれるGPUのダイが八つ一つのパッケージに封入されている。そうした手法をとるのは、半導体の製造は大きなダイを一つ製造するよりも、小さなダイを複数製造する方が、歩留まり(良品率)が向上するなど効率が良いからだ。

しかし、今回NVIDIAは大胆にもH100よりもさらに大きなダイサイズのチップ二つをパッケージに封入するという手法を取っている。つまり、製造時の効率よりもとにかく性能を重視してこうした設計にしていると言えるだろう。AMDのようにダイを増やすと、ダイとダイが通信する量が増えて、結果的にパッケージ全体の処理がそうしたチップ間の通信に取られてしまって性能が上がらないことは考えられる。それを最小限にする意味でも大きなダイを二つという考え方は性能を重視するなら妥当な選択だ。なお、二つのダイは10TB/秒の帯域幅を実現しているNV-HDIと呼ばれる独自の内部バスで接続されている。

こうしたダイを二つ実装するメリットは単純な性能が向上する以外にも、一つのパッケージあたりのメモリコントローラが倍になるというメリットがある。このためH100世代のフルスペックでは、12×512ビットのメモリバス構成が可能になっていたが、SXMでは10×512ビットという構成になっている。Blackwellの一つのダイあたりのメモリバス構成などは公開されていないが、やはり一つのダイあたり12×512ビットないしは10×512ビットという構成になっていると考えられる。それが二つのダイで2倍の構成になるため、B200のスペックを見る限り、一つのチップに192GBのHBM3eが実装する形になっているので、一つのダイあたり96GBのHBMという計算になるので、おそらく12×512ビットと考えるのが妥当だろう。メモリ帯域も2倍以上に引き上げられており、H100では3.35TB/秒だったのが、B200では8TB/秒となっている。

■FP64の性能はH100に比べて約32%しか向上しないが、FP8(Tensorコア)では約2.5倍になっている

今回NVIDIAは、こうしたBlackwellのダイそのもののマイクロアーキテクチャに関してはほとんど公開していない。わずかに公開されたことは、新しい800GB/秒のスループットを実現する解凍エンジン、暗号化やTEEなどのコンフィデンシャルコンピューティングに対応していること、RSAエンジンを搭載していることなどで、内部の演算器の構成がどうなっているのか(SMはいくつあるのか、CUDAコアはいくつあるのか)などに関して全く説明しておらず、それらに関しては後日公開するとだけ説明している。

その中で唯一説明があったのが、H100世代で導入された「Transformer Engine」(AIの学習や推論に特化した演算器)が第2世代になり、第1世代では対応していなかったFP6とFP4というより低精度の浮動小数点演算に対応したことだ。よく知られている通り、特にAI推論では精度の低い整数や浮動小数点で演算しても、正確性にはあまり影響がない。このため、AI推論の演算を低精度の整数や浮動小数点を利用して演算することがトレンドになっており、従来はBF16やFP16で行なっていたAI推論をINT8やFP8で推論をするというのが一般的になっている。最近ではさらにFP4や、さらにそれ以下での演算も研究が進んでいるが、今回のBlackwellの第2世代Transformer EngineではFP6とFP4という新しい精度に対応したことになる。

その効果は絶大でFP4(Tensorコア)で演算した場合には20PFLOPSという性能になるので、H100 SXMのFP8(Tensorコア)の約4PFLOPSと比較すると約5倍になっている。例えば、従来H100のFP8で行なっていた推論処理を、そのままBlackwellのFP4に置きかえるだけで性能が5倍になるということを意味するので、その効果は大きいと言える。また、同じFP8(Tensorコア)で比較すると、約2.5倍となる。

ただ、Tensorコアではない、通常の浮動小数点演算の性能はあまり上がっていない。H100 SXMで34TLOPSだったFP64は、Blackwellでは45TFLOPSでしかない。単純計算で約32%しか向上していない計算になる。FP32もおそらく同じような性能向上になるだろう。HPCでは一般的にFP64やFP32を使うことを考えると、そうした一般的なHPCアプリケーションに使うユーザーがH100からBlackwellに乗り換えるメリットは従来の新世代登場の時よりは少ないと言わざるを得ないだろう。逆に言えば、そうしたユーザーは現行のH100 SXMベースの製品を安心して購入できると言える。

しかし、FP8(Tensorコア)の性能が約2.5倍と大きく向上していることからもわかるように、Blackwellは基本的にAI処理に利用することを前提にしたGPUだと考えると、フアン氏が「われわれは生成 AI 時代のプロセッサーを作った」と表現したことは妥当な表現だし、そのターゲットを明確に示している。

■TDP枠の違いで三つのグレードが用意されている、Grace CPUと1ボードのGB200も用意されている

現時点ではBlackwellベースの製品は三つのグレードがある。具体的にはTDP1200WのB200、TDP1000WのB200、そしてTDP700WのB100の3製品だ。

| B200(GB200版) | B200(DGX/HGX版) | B100(HGX版) | Hopper(H100 SXM) | |

| ダイ/パッケージ | 2 | 2 | 2 | 1 |

| FP64 | 45TFLOPS | 40TFOPS | 30TFOPS | 34TFLOPS |

| TF32(Tensorコア) | 2.5PFLOPS | 2.2PFLOPS | 1.8PFLOPS | 989TFLOPS |

| FP16/BF16(Tensorコア) | 5PFLOPS | 4.5PFLOPS | 3.5PFLOPS | 1.979PFLOPS |

| FP8/FP6/INT8(Tensorコア) | 10PFLOPS | 9PFLOPS | 7PFLOPS | 3.958PFLOPS |

| FP4(Tensorコア) | 20PFLOPS | 18PFLOPS | 14PFLOPS | - |

| GPUメモリ | 最大192GB(HBM3e) | 最大192GB(HBM3e) | 最大192GB(HBM3e) | 80GB(HBM3) |

| GPUメモリ帯域幅 | 8TB/秒 | 8TB/秒 | 8TB/秒 | 3.35TB/秒 |

| NVLink | 第5世代 | 第5世代 | 第5世代 | 第4世代 |

| NVLink帯域幅 | 1.8TB/秒(双方向) | 1.8TB/秒(双方向) | 1.8TB/秒(双方向) | 900GB/秒(双方向) |

| TDP | 1200W | 1000W | 700W |

700W |

表2:Blackwellの三つの製品(NVIDIA社の資料などより筆者作成)

いずれの製品も二つのダイが1チップで、HBM3e/192GBのメモリを搭載しているという点では同じだ。違いはなんなのかと言えば、TDP(Thermal Design Power、熱設計消費電力)の枠の違いだ。TDPというのはピーク時の消費電力ではなく、その電力が半導体にかかった時に発生する熱を排熱できるように、どう設計したらいいのかをOEMメーカーが示唆する指標となる数字だ。今回NVIDIAはB200に1200Wと1000Wという二つのTDPを設定しており、前者は液冷向け、後者は空冷向けと位置づけている。また、従来のH100 SXMと同じ700Wの枠になるB100も設定しており、OEMメーカーが700W向けの空冷設計を使い回せるように配慮している。当然だが、TDPの枠をあげればあげるほど、クロック周波数や有効にする演算器の数を増やせるので性能は向上する。実際FP4(Tensorコア)の性能はB200/1200Wが20PFLOPS、B200/1000Wが18PFLOPS、そしてB100/700Wは14PFLOPSとなっている。このあたりは性能と価格でどれを選ぶか決めるということになるだろう。

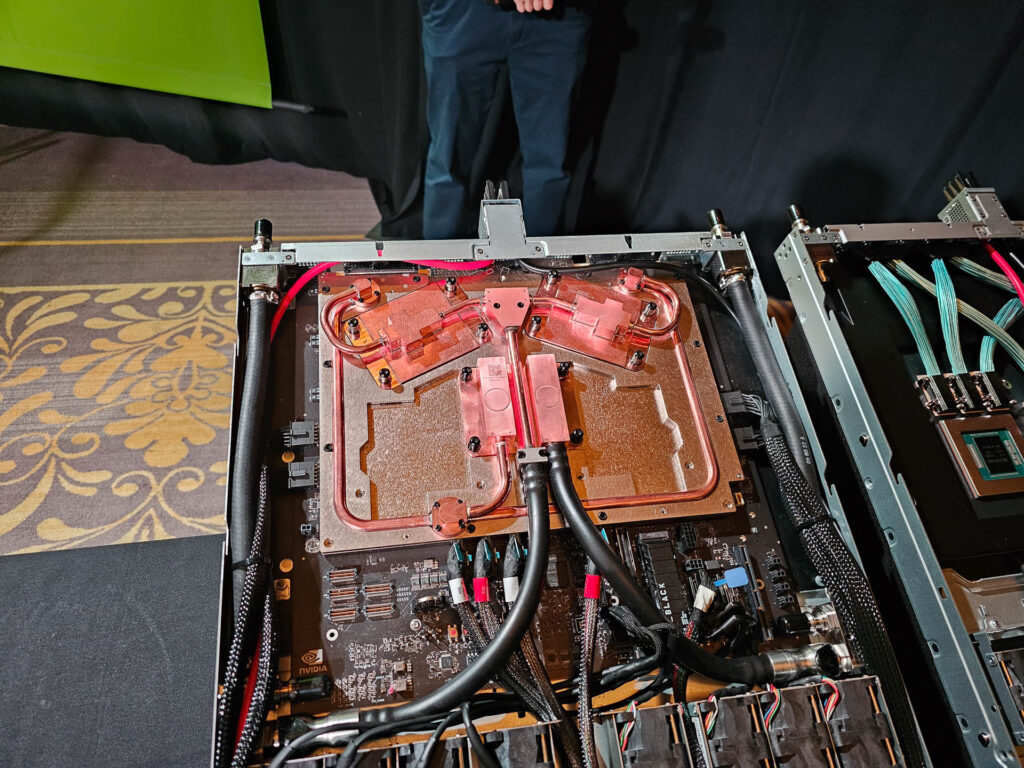

なお、NVIDIAはこうしたBlackwell単体以外にも、Hopper世代のGrace Hopper(NVIDIA GH200 Superchip、以下GH200)のようなArm CPUであるGraceと1モジュールにした製品も用意しており、それがGrace BlackwellことNVIDIA GB200 Superchip(以下GB200)だ。GH200ではCPUのGraceが一つ、GPUのHopperが一つという構成になっていたが、GB200ではCPUのGraceが一つは変わらないのだが、GPUのBlackwellは二つになっている。かつ、このBlackwellは1200W版B200になっており、冷却は液冷が事実上必須となる。

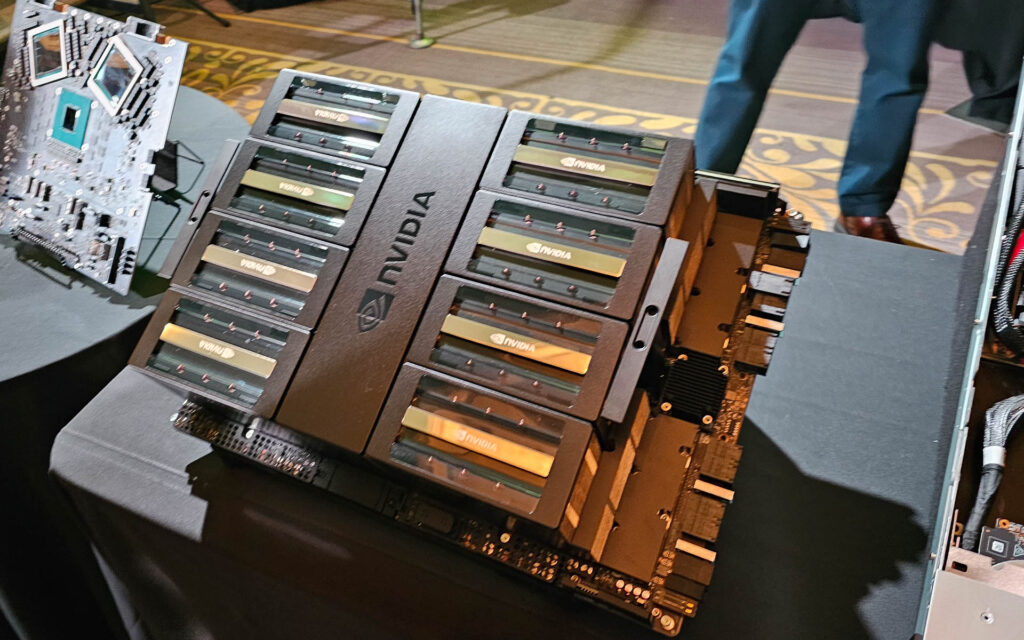

■DGX B200、HGX B200、HGX B100、GB200 NVL72などのサーバー/ラックサーバー製品群も同時に発表

こうしたソリューションを採用したサーバー製品として、NVIDIAは自社ブランドのDGXとしてDGX B200、そしてOEMメーカーが販売するHGXとしてHGX B200、HGX B100を用意している。それに加えて、GB200のボード36枚を1ラックにまとめたGB200 NVL72、そしてそのDGX版となるDGX GB200 NVL72を用意している。このうちDGX B200、HGX B200、HGX B100は空冷となり、採用されているBlackwellは前者二つがB200/1000W、後者がB100となる。そしてGB200 NVL72に関しては液冷となり、液冷の仕組みもOEMメーカーなりNVIDIAから提供される形となる。

| DGX B200 | HGX B200 | HGX B100 | GB200 NVL72(DGX GB200 NVL72) | |

| GPU | B200×8 | B200×8 | B100×8 | GB200x72 |

| CPU | 第5世代Xeon×2 | x86/Arm | x86/Arm | Grace(Arm)×36 |

| 冷却方式 | 空冷 | 空冷 | 空冷 | 液冷 |

| FP4(Tensorコア) | 144PFLOPS | 144PFLOPS | 112PFLOPS | 1.4EFLOPS |

| FP8/FP6/INT8(Tensorコア) | 72PFLOPS | 72PFLOPS | 56PFLOPS | 720PFLOPS |

| GPUメモリ(合計) | 1.5TB | 1.5TB | 1.5TB | 13.5TB |

表3:Blackwellを採用したサーバー、ラックサーバー製品(NVIDIA社の資料などより筆者作成)

特にGB200 NVL72はBlackwellが72基、ラックの中でスケールアップされている。それが可能になったのは、BlackwellのNVLinkが第5世代に強化されて、Hopper世代の900GB/秒(双方向)から1.8TB/秒(双方向)へと強化されているからだ。さらに新しいNV Switchと組み合わせるとHopper世代では最大で256基までスケールアップできる仕様だったが、Blackwell世代では576基までスケールアップできるようになっている。GB200 NVL72ではそれを利用して72基までラックの中でスケールアップすることで、FP4(Tensorコア)で1.4EFLOPSという性能を実現している。

なおこうしたDGXやGB200 NVL72などを組み合わせて、NVIDIAのInfiniBandやイーサネットを利用してスケールアウトすることでスーパーコンピューターを構成する「SuperPod」ももちろん提供される。

NVIDIAによれば、これらの新製品は英語で言うと「Later this year」、日本語にすると年内という出荷予定時期が明らかにされている。H100の時は、2022年に発表はされたが、製品の出荷が始まったのは23年に入ってからで1年近くかかったが、今回はそれよりは早く出荷させることを期待していいのではないだろうか。

笠原一輝